# decsystem-1080/1090 SYSTEM DESCRIPTION

1st Edition, June 1975 2nd Printing, April 1976 3rd Edition, (Rev) January 1977

The drawings and specifications herein are the property of Digital Equipment Corporation and shall not be reproduced or copied or used in whole or in part as the basis for the manufacture or sale of equipment described herein without written permission.

Copyright © 1975, 1976, 1977 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice. Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

This document was set on DIGITAL's DECset-8000 computerized typesetting system.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

DEC DECtape PDP

DECCOMM DECUS RSTS

DECsystem-10 DIGITAL TYPESET-8

DECSYSTEM-20 MASSBUS TYPESET-11

UNIBUS

### **CONTENTS**

|           |                              | Page       |

|-----------|------------------------------|------------|

| SECTION 1 | PRINCIPLES OF TIME-SHARING   |            |

| 1.1       | INTRODUCTION                 | SYS10/1-1  |

| 1.2       | OPERATION                    |            |

| 1.2.1     | Dynamic Scheduling           |            |

| 1.2.2     | Software Sharing             |            |

| 1.2.3     | Communications               | ,          |

| 1.2.4     | Control of Input/Output      |            |

| 1.2.5     | File Handling                |            |

| 1.2.6     | Slow Peripherals             | ,          |

| 1.3       | RELIABILITY                  |            |

| SECTION 2 | DECsystem-10 PRIMER          |            |

| 2.1       | INTRODUCTION                 | SYS10/2-1  |

| 2.2       | HARDWARE                     |            |

| 2.3       | OPERATING SYSTEM             |            |

| 2.4       | NONRESIDENT SOFTWARE         |            |

| 2.5       | MULTIPROCESSING              |            |

| 2.6       | MULTIMODE COMPUTING          |            |

| 2.6.1     | Time-Sharing                 | SYS10/2-4  |

| 2.6.1.1   | Command Language             |            |

| 2.6.1.2   | Peripheral Devices           | SYS10/2-5  |

| 2.6.1.3   | Spooling                     | SYS10/2-5  |

| 2.6.1.4   | Mass Storage File System     | SYS10/2-5  |

| 2.6.1.5   | Core Utilization             | SYS10/2-5  |

| 2.6.1.6   | General-Purpose Time-Sharing |            |

| 2.6.2     | Batch                        | SYS10/2-6  |

| 2.6.2.1   | Components                   | SYS10/2-6  |

| 2.6.2.2   | Use of System Features       | SYS10/2-8  |

| 2.6.2.3   | Flexibility                  | SYS10/2-8  |

| 2.6.2.4   | Job Dependency               | SYS10/2-8  |

| 2.6.2.5   | Error Recovery               | SYS10/2-8  |

| 2.6.2.6   | Operator Intervention        | SYS10/2-8  |

| 2.6.3     | Real-Time                    | SYS10/2-9  |

| 2.6.3.1   | Locking Jobs                 | SYS10/2-9  |

| 2.6.3.2   | Real-Time Devices            | SYS10/2-9  |

| 2.6.3.3   | High-Priority Run Queues     |            |

| 2.6.3.4   | Job Communication            | SYS10/2-10 |

|           |                                     | rage     |

|-----------|-------------------------------------|----------|

| SECTION 3 | SYSTEM FEATURES                     |          |

| 3.1       | CENTRAL PROCESSOR                   | YS10/3-1 |

| 3.2       |                                     | YS10/3-1 |

| 3.2.1     |                                     | YS10/3-4 |

| 3.2.2     |                                     | YS10/3-4 |

| 3.2.3     |                                     | YS10/3-4 |

| 3.2.4     |                                     | YS10/3-4 |

| 3.2.5     |                                     | YS10/3-4 |

| 3.2.6     |                                     | YS10/3-5 |

| 3.2.7     |                                     | YS10/3-5 |

| 3.2.8     |                                     | YS10/3-5 |

| 3.2.9     |                                     | YS10/3-5 |

| 3.2.10    |                                     | YS10/3-5 |

| 3.2.11    |                                     | YS10/3-5 |

| 3.2.12    | ·                                   | YS10/3-6 |

| 3.2.13    |                                     | YS10/3-6 |

| 3.2.14    | •                                   | YS10/3-6 |

| 3.2.15    |                                     | YS10/3-6 |

| 3.3       |                                     | YS10/3-6 |

| 3.4       |                                     | YS10/3-6 |

| 3.4.1     |                                     | YS10/3-7 |

| 3.4.2     |                                     | YS10/3-7 |

| 3.5       |                                     | YS10/3-8 |

| 3.6       |                                     | YS10/3-8 |

| 3.7       |                                     | YS10/3-8 |

| 3.7.1     |                                     | YS10/3-8 |

| 3.7.2     |                                     | YS10/3-9 |

| 3.8       |                                     | YS10/3-9 |

| 3.9       | PROCESS TABLES                      |          |

| 3.10      | MEMORY PROTECTION AND RELOCATION SY | S10/3-10 |

| 3.11      | DIRECT I/O                          |          |

| 3.12      | CHANNEL I/O                         |          |

| 3.12.1    | External Data Channels              |          |

| 3.12.2    | Integrated Data Channels            |          |

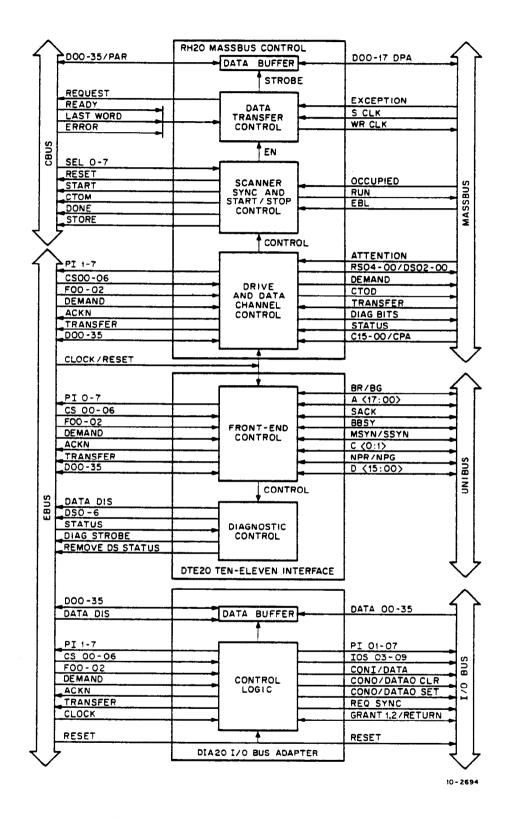

| 3.12.2.1  | Massbus Controller                  |          |

| 3.12.2.2  | Channel Controllers                 |          |

| 3.13      | PRIORITY INTERRUPT SYSTEM SY        | S10/3-16 |

| 3.14      | TRAP FACILITY                       | S10/3-17 |

| 3.15      | PROGRAMMABLE CLOCKS                 | S10/3-17 |

| 3.16      | CONSOLE/DIAGNOSTIC COMPUTER         | S10/3-18 |

| 3.17      | SYSTEM INTEGRITY FEATURES           | S10/3-18 |

Page **SECTION 4** THE HARDWARE 4.1 **CONFIGURATIONS** 4.2 SYS10/4-1 4.2.1 4.2.1.1 Hardware ..... SYS10/4-9a 4.2.1.2 4.2.2 MBox 4.2.3 4.2.4 4.2.5 4.2.5.1 Read Operations 4.2.5.2 Write Operations 4.2.53 Read-Pause-Write Operation . . . . . . . . . . . . . . . . . SYS10/4-30 4.2.6 DMA20 4.2.7 4.2.7.1 4.2.7.2 4.2.7.3 Programmable Interrupt (PI1-7) Operation . . . . . . . SYS10/4-34 4.2.7.4 High Priority (PIO) Interrupt Operation . . . . . . . . . . SYS10/4-35 4.2.8 4.2.9 4.2.10 RH20 4.2.11 DIA20 4.2.12 4.2.13 4.2.14 Internal Devices 4.2.14.1 4.2.14.2 4.2.14.3 4.2.14.4 4.2.14.5 TIM and MTR 4.2.15 External and Internal I/O Controllers and Devices 4.2.16 4.3 CONSOLE PROCESSOR SUBSYSTEM . . . . . . . . . . . . . . . . . SYS10/4-41 4.3.1 4.3.1.1 KD11-A Central Processor · · · · · · · · · · · · · · · · · · SYS10/4-42 4.3.1.2 KY11-D Programmer's Console . . . . . . . . . . . . . . . SYS10/4-42 4.3.1.3 KW11-L Line Clock Option . . . . . . . . . . . . . . . . SYS10/4-42 4.3.1.4 MF11-UP Memory 4.3.1.5 MM11-UP Memory 4.3.1.6 BM873-YD/YG ROM Loader Module .... SYS10/4-42 4.3.1.7 DL11-C Asynchronous Line Interface . . . . . . . . . . SYS10/4-43 4.3.1.8 DL11-E Asynchronous Line Interface . . . . . . . . . SYS10/4-43

|          |                                                    | Page                    |

|----------|----------------------------------------------------|-------------------------|

| 4.3.1.9  | LA36 Keyboard Terminal                             | SYS10/4-43              |

| 4.3.1.10 | RJP04/06 Disk File System                          | . SYS10/4-43            |

| 4.3.1.11 | TC11-G Magnetic Tape System                        | SYS10/4-43              |

| 4.3.1.12 | BC11-A Unibus                                      |                         |

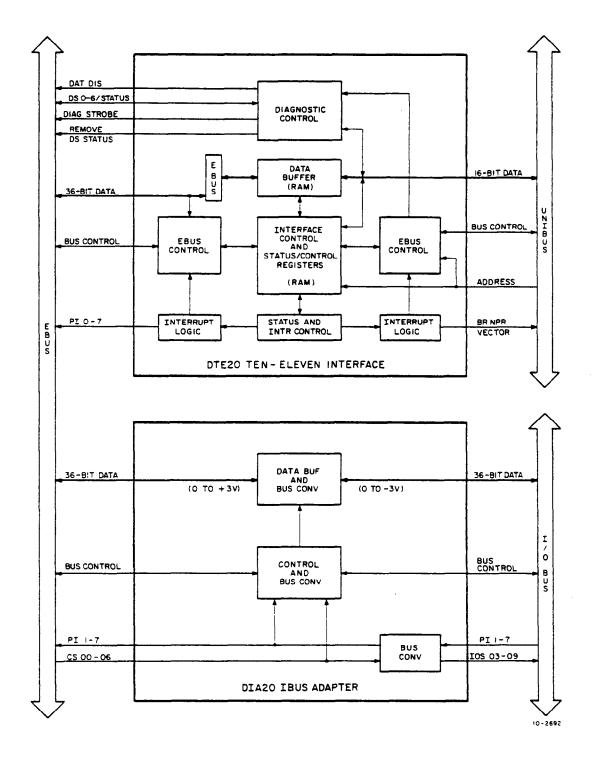

| 4.3.1.13 | DTE20 Ten-Eleven (Console/Front-End Processor)     |                         |

|          | Interface                                          | SYS10/4-43              |

| 4.3.2    | Interdevice Transfers                              | SYS10/4-44              |

| 4.3.3    | Functions                                          | SYS10/4 <del>-4</del> 4 |

| 4.3.3.1  | Examine/Deposit Operations                         | . SYS10/4-44            |

| 4.3.3.2  | TO10/TO11 Byte Transfer Operations                 |                         |

| 4.3.3.3  | Interprocessor Interrupts                          |                         |

| 4.3.3.4  | Diagnostic and Miscellaneous Console Functions     |                         |

| 4.3.3.5  | System Bootstrap Function                          | SYS10/4-46              |

| 4.3.4    | Modes                                              | SYS10/4-46              |

| 4.3.5    | Interprocessor Communications                      | •                       |

| 4.3.5.1  | Communication Areas                                | . SYS10/4-47            |

| 4.3.5.2  | Queue Processing/Messages                          | · ·                     |

| 4.4      | MAIN MEMORY SUBSYSTEM                              |                         |

| 4.5      | SECONDARY MEMORY SUBSYSTEMS                        |                         |

| 4.5.1    | Disk Subsystems                                    |                         |

| 4.5.1.1  | RHP04/06 and RTP04/06 Disk Subsystem               |                         |

| 4.5.1.2  | RHS04 Disk Subsystem                               |                         |

| 4.5.2    | Magnetic Tape Subsystem                            |                         |

| 4.5.2.1  | TU70/71/72 Magnetic Tape Subsystem                 |                         |

| 4.5.2.2  | THU16/TTU16 Magnetic Tape Subsystem                |                         |

| 4.5.2.3  | TU56 DECtape Subsystem                             |                         |

| 4.6      | BA10 UNIT RECORD (HARD COPY) EQUIPMENT             |                         |

| 4.6.1    | CR10 Card Reader                                   |                         |

| 4.6.2    | LP10 Line Printer                                  | · ·                     |

| 4.6.3    | CP10-D Card Punch                                  |                         |

| 4.6.4    | XY10 Plotter                                       |                         |

| 4.7      | LP100 LINE PRINTER SUBSYSTEM                       |                         |

| 4.8      | COMMUNICATIONS SUBSYSTEMS                          |                         |

| 4.8.1    | Communication Primer                               |                         |

| 4.8.2    | DC76 Asynchronous Communication Subsystem          |                         |

| 4.8.3    | DC75-NP Synchronous Communications Subsystem       |                         |

| 4.8.4    | DN87/DN87S Universal Synchronous/Asynchronous      |                         |

|          | Front-End Subsystems                               | SYS10/4-61              |

| 4.8.4.1  | Asynchronous Interfaces                            |                         |

| 4.8.4.2  | Synchronous Interfaces                             |                         |

| 4.8.5    | Communication Subsystem Components                 | SYS10/4-62              |

| 4.8.5.1  | KG11-A XOR and CRC Unit (DC75-NP, DN87,            |                         |

|          | and DN87S)                                         | . SYS10/4-62            |

| 4.8.5.2  | DS11 Multiple Line Synchronous Interface (DC75-NP) | SYS10/4-64              |

|          |                                                    |                         |

| 4.8.5.3       DH11 Asynchronous 16-Line Multiplexer (DC76, DN87, and DN87S)       SYS10/4-64         4.8.5.4       DM11-BB Modem Control Unit (DC76, DN87, and DN87S)       SYS10/4-65         4.8.5.5       DQ11 Synchronous Line Interface (DN87 and DN87S)       SYS10/4-65         4.8.6       DC72-NP Remote Station       SYS10/4-66         4.8.7       DN80 (DAS80)-Series Remote Station       SYS10/4-67         4.8.8       DAS92 Remote Station       SYS10/4-69         SECTION 5         THE SOFTWARE         5.1       RESIDENT OPERATING SYSTEM       SYS10/5-1         5.1.1       Command Decoder       SYS10/5-3         5.1.2       Scheduler       SYS10/5-3 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.8.5.4       and DN87S)       SYS10/4-64         4.8.5.4       DM11-BB Modem Control Unit (DC76, DN87, and DN87S)       SYS10/4-65         4.8.5.5       DQ11 Synchronous Line Interface (DN87 and DN87S)       SYS10/4-65         4.8.6       DC72-NP Remote Station       SYS10/4-66         4.8.7       DN80 (DAS80)-Series Remote Station       SYS10/4-67         4.8.8       DAS92 Remote Station       SYS10/4-69         SECTION 5       THE SOFTWARE         5.1       RESIDENT OPERATING SYSTEM       SYS10/5-1         5.1.1       Command Decoder       SYS10/5-3                                                                                                    |

| 4.8.5.4       DM11-BB Modem Control Unit (DC76, DN87, and DN87S)       SYS10/4-65         4.8.5.5       DQ11 Synchronous Line Interface (DN87 and DN87S)       SYS10/4-65         4.8.6       DC72-NP Remote Station       SYS10/4-66         4.8.7       DN80 (DAS80)-Series Remote Station       SYS10/4-67         4.8.8       DAS92 Remote Station       SYS10/4-69         SECTION 5       THE SOFTWARE         5.1       RESIDENT OPERATING SYSTEM       SYS10/5-1         5.1.1       Command Decoder       SYS10/5-3                                                                                                                                                      |

| 4.8.5.5       DQ11 Synchronous Line Interface (DN87 and DN87S)       SYS10/4-65         4.8.6       DC72-NP Remote Station       SYS10/4-66         4.8.7       DN80 (DAS80)-Series Remote Station       SYS10/4-67         4.8.8       DAS92 Remote Station       SYS10/4-69         SECTION 5       THE SOFTWARE         5.1       RESIDENT OPERATING SYSTEM       SYS10/5-1         5.1.1       Command Decoder       SYS10/5-3                                                                                                                                                                                                                                                |

| 4.8.6       DC72-NP Remote Station       SYS10/4-66         4.8.7       DN80 (DAS80)-Series Remote Station       SYS10/4-67         4.8.8       DAS92 Remote Station       SYS10/4-69         SECTION 5       THE SOFTWARE         5.1       RESIDENT OPERATING SYSTEM       SYS10/5-1         5.1.1       Command Decoder       SYS10/5-3                                                                                                                                                                                                                                                                                                                                        |

| 4.8.7       DN80 (DAS80)-Series Remote Station       SYS10/4-67         4.8.8       DAS92 Remote Station       SYS10/4-69         SECTION 5       THE SOFTWARE         5.1       RESIDENT OPERATING SYSTEM       SYS10/5-1         5.1.1       Command Decoder       SYS10/5-3                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4.8.8 DAS92 Remote Station SYS10/4-69  SECTION 5 THE SOFTWARE  5.1 RESIDENT OPERATING SYSTEM SYS10/5-1 5.1.1 Command Decoder SYS10/5-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4.8.8       DAS92 Remote Station       SYS10/4-69         SECTION 5       THE SOFTWARE         5.1       RESIDENT OPERATING SYSTEM       SYS10/5-1         5.1.1       Command Decoder       SYS10/5-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5.1       RESIDENT OPERATING SYSTEM       SYS10/5-1         5.1.1       Command Decoder       SYS10/5-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5.1.1 Command Decoder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5.1.1 Command Decoder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.1.3 Swapper                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5.1.4 Control Routine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5.1.5 UUO Handler SYS10/5-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5.1.6 Device Service Routines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5.1.7 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5.2 COMMAND CONTROL LANGUAGE SYS10/5-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5.3 FILE SYSTEM SYS10/5-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5.3.1 File Handler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5.3.2 File Structures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5.3.3 File Protection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5.3.4 Disk Quotas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5.3.5 File Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5.3.6 Disk Storage Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5.4 INPUT/OUTPUT SYS10/5-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5.4.1 Peripheral Device Assignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5.4.2 Spooling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.5 MEMORY MANAGEMENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5.5.1 Secondary Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5.5.2 Reentrant Software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5.5.3 Virtual Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5.6 MULTIPROCESSING SYSTEMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5.7 INTERJOB COMMUNICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5.7.1 Shared Data Areas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5.7.2 Interprocess Communication Facility                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5.8 NONRESIDENT SYSTEM SOFTWARE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.8.1 MACRO Assembler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5.8.2 Compilers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.8.2.1 ALGOL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5.8.2.2 BASIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5.8.2.3 COBOL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5.8.2.4 FORTRAN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                  | Page                                                      |

|------------------|-----------------------------------------------------------|

| 5.8.3            | Interpreters                                              |

| 5.8.3.1          | AID                                                       |

| 5.8.3.2          | APL                                                       |

| 5.8.3.3          | CPL                                                       |

| 5.8.4            | Editors                                                   |

| 5.8.4.1          | LINED SYS10/5-18                                          |

| 5.8.4.2          | TECO                                                      |

| 5.8.4.3          | SOUP                                                      |

| 5.8.4.4          | RUNOFF                                                    |

| 5.8.5            | Utilities                                                 |

| 5.8.5.1          | CREF                                                      |

| 5.8.5.2          | DBMS-10                                                   |

| 5.8.5.3          | DDT SYS10/5-20                                            |

| 5.8.5.4          | FAILSAFE/BACKUP                                           |

| 5.8.5 <i>.</i> 5 | FILEX SYS10/5-20                                          |

| 5.8.5.6          | ITPS-10 SYS10/5-21                                        |

| 5.8.5.7          | LINK-10 SYS10/5-21                                        |

| 5.8.5 <i>.</i> 8 | PIP                                                       |

| 5.8.5.9          | MACY11 and LNKX11                                         |

| 5.8.5.10         | MCS-10                                                    |

| 5.8.6            | Monitor Support Programs                                  |

| 5.8.6.1          | MONGEN                                                    |

| 5.8.6.2          | OPSER                                                     |

| 5.8.6.3          | LOGIN                                                     |

| 5.8.6.4          | KJOB-LOGOUT SYS10/5-23                                    |

| 5.9              | CONSOLE SOFTWARE                                          |

| 5.9.1            | Basic Command Facility Description                        |

| 5.9.2            | General System Bootstrap                                  |

| 5.9.3            | Diagnostic Environments                                   |

| 5.9.4            | Diagnostic Options                                        |

| 5.9.5            | System Failure Procedures                                 |

| 5.10             | COMMUNICATION SOFTWARE                                    |

| 5.11             | DIAGNOSTIC SOFTWARE                                       |

| 5.11.1           | Operating System Features                                 |

| 5.11.2           | Integrated Diagnostic Logic                               |

| 5.11.3           | On-Line Preventive Maintenance                            |

| 5.11.4           | Remote Diagnosis                                          |

| 5.11.5           | Monitor Error Reporting Programs                          |

| 5.11.5.1         | Overview of the Monitor Error Reporting System SYS10/5-28 |

| 5.11.5.2         | Hardware Error Information                                |

| 5.11.5.3         | Reporting Programs                                        |

| 5.11.5.4         | Testing Programs                                          |

| 5.11.6           | Diagnostic Programs                                       |

|                  |                                                           |

APPENDIX A ABBREVIATIONS AND MNEMONICS

## **FIGURES**

| Figure No. | Title                                                    | Page       |

|------------|----------------------------------------------------------|------------|

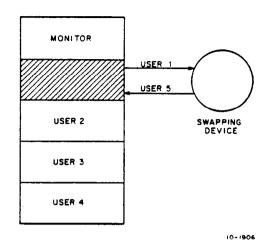

| 1-1        | Swapping of User Programs                                | SYS10/1-3  |

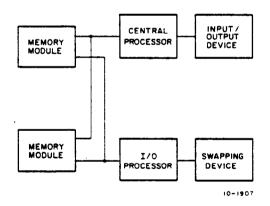

| 1-2        | Memory Structure                                         |            |

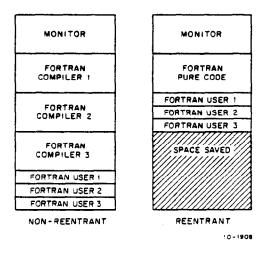

| 1-3        | Software Types                                           | SYS10/1-4  |

| 1-4        | User/Computer Communications                             |            |

| 1-5        | File Structure                                           | SYS10/1-7  |

| 2-1        | DECsystem-10 Components                                  | SYS10/2-1  |

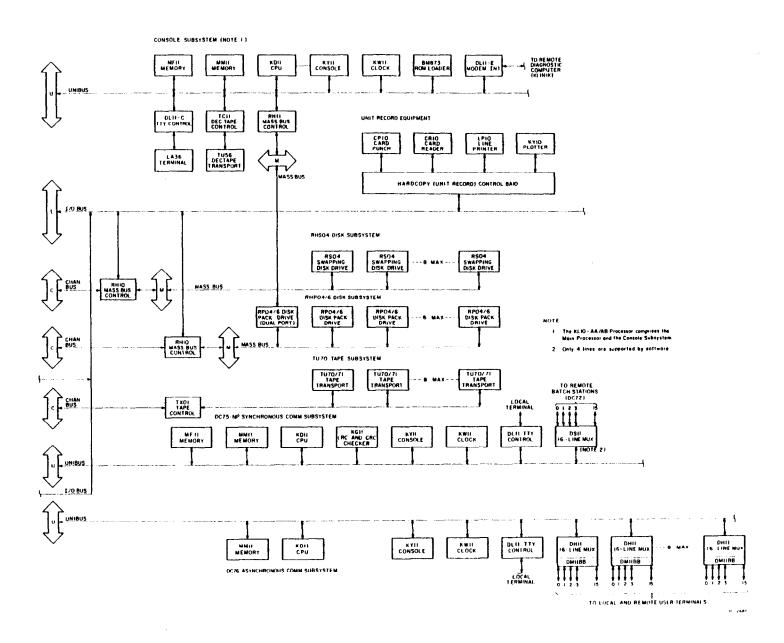

| 2-2        | A Typical DECsystem-1080                                 |            |

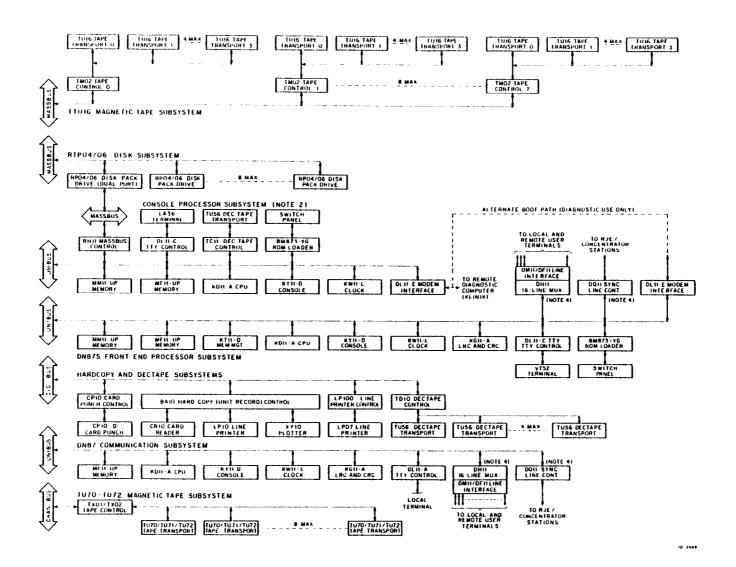

| 2-3        | A Typical DECsystem-1090                                 |            |

| 2-4        | Programs in the Batch System                             | SYS10/2-7  |

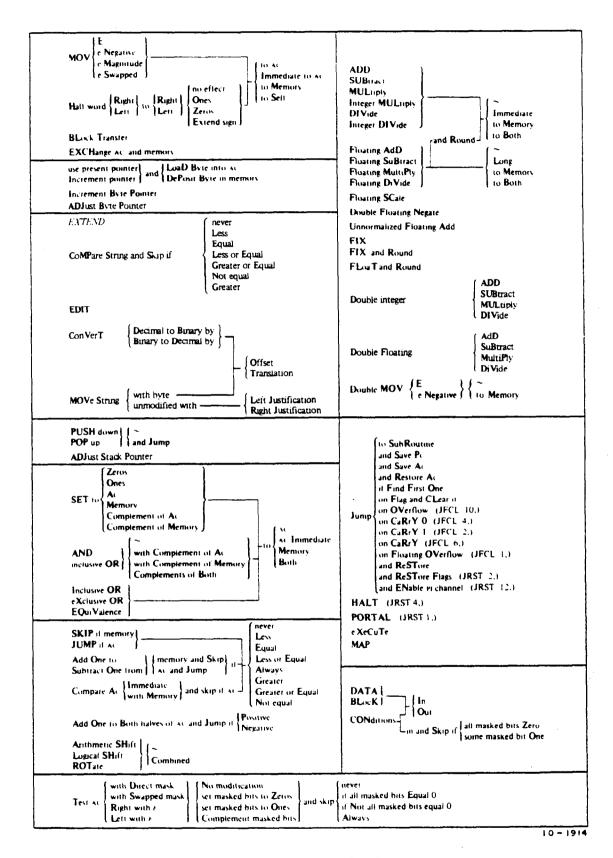

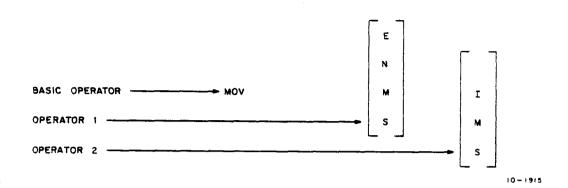

| 3-1        | Instruction Set Constructs                               | SYS10/3-3  |

| 3-2        | Move Instruction Construct                               | SYS10/3-4  |

| 3-3        | Instruction Format                                       |            |

| 3-4        | User Process Table                                       |            |

| 3-5        | Executive Process Table                                  |            |

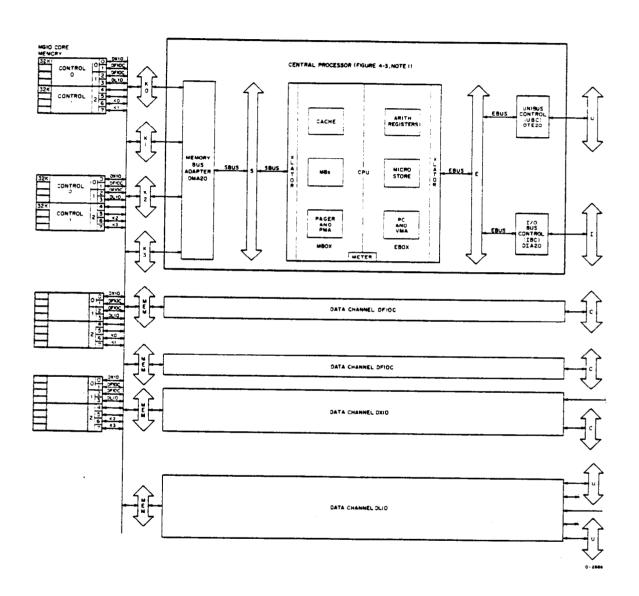

| 4-l        | DECsystem-1080 (Typical) Block Diagram                   |            |

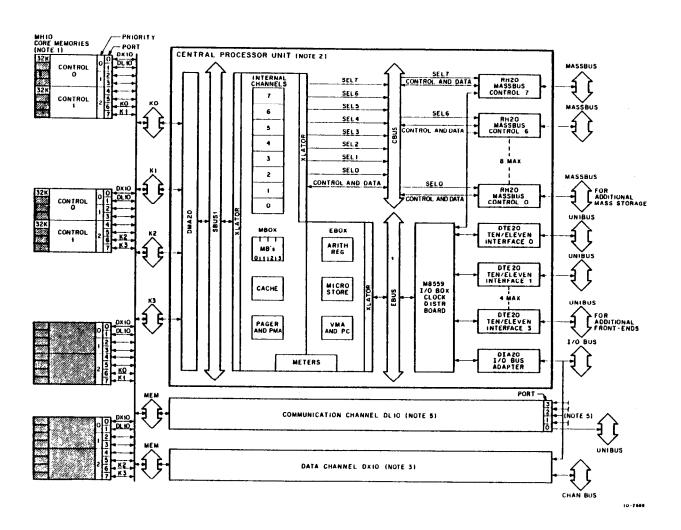

| 4-2        | DECsystem-1090 (Typical) Block Diagram                   |            |

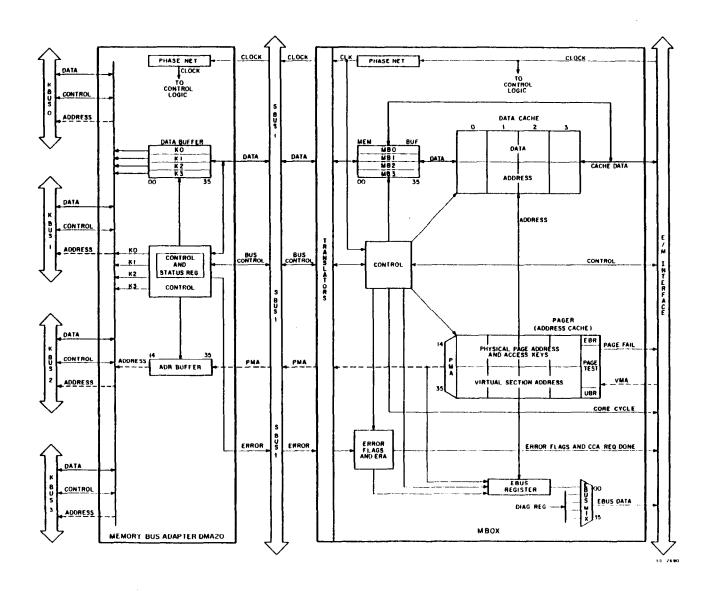

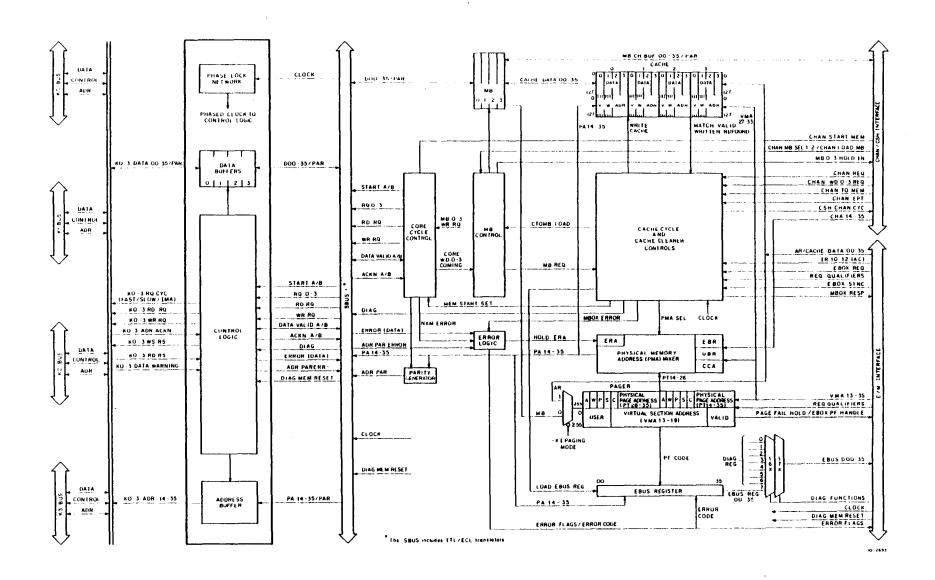

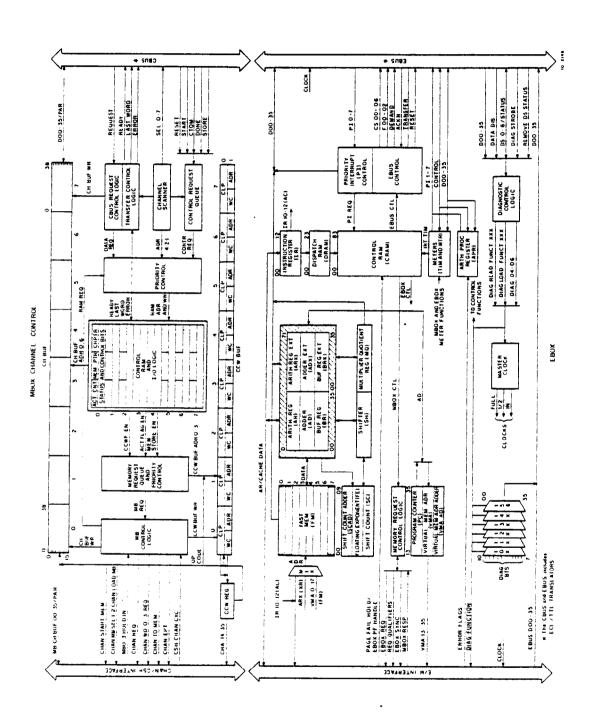

| 4-3        | DECsystem-1080 Central Processor Subsystem Block Diagram | SYS10/4-11 |

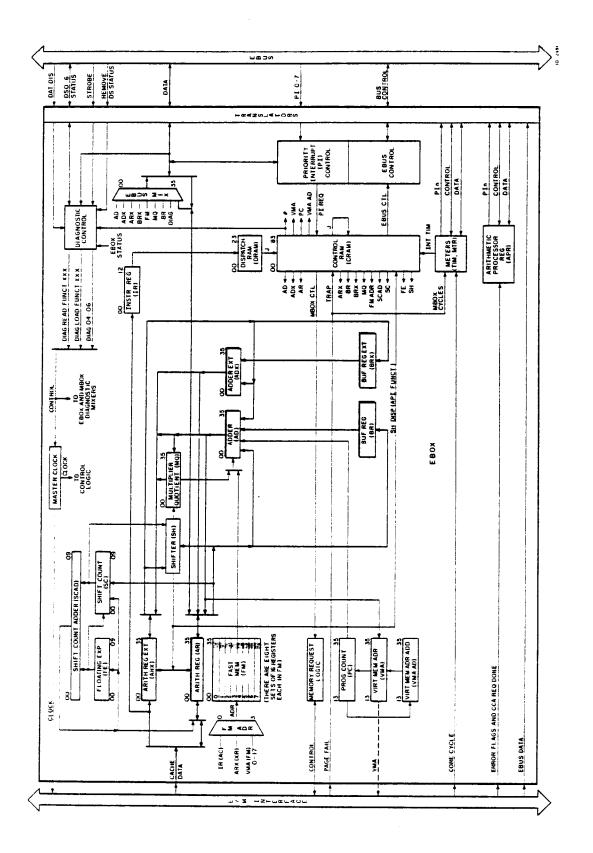

| 4-4        | DECsystem-1090 Central Processor Subsystem Block Diagram | SYS10/4-17 |

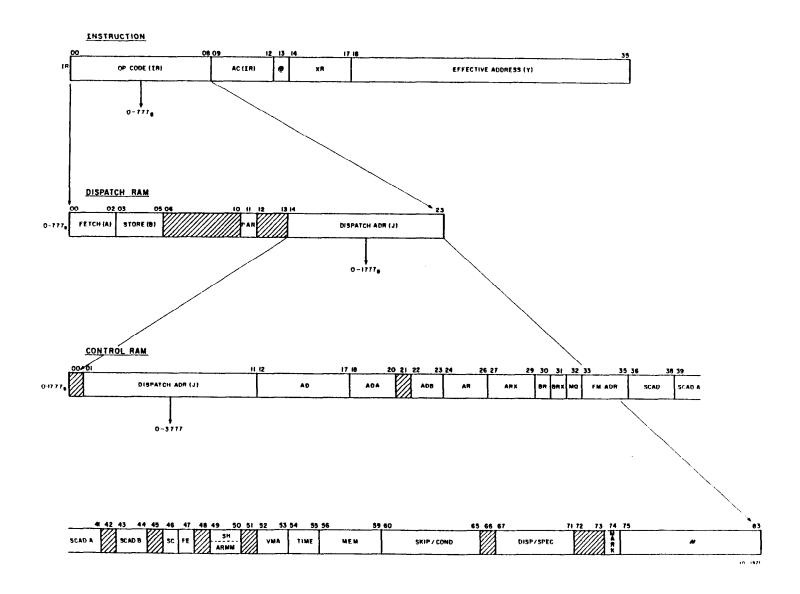

| 4-5        | Instruction, Dispatch, and Control Formats               | SYS10/4-26 |

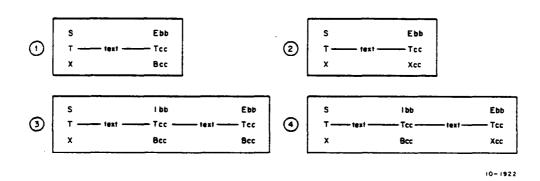

| 4-6        | IBM Compatible Message Format                            | SYS10/4-63 |

| 4-7        | BCC Computation for Transparent Transmission             | SYS10/4-63 |

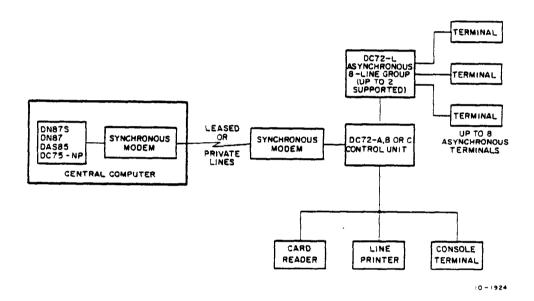

| 4-8        | DC72-NP Remote Station                                   | SYS10/4-66 |

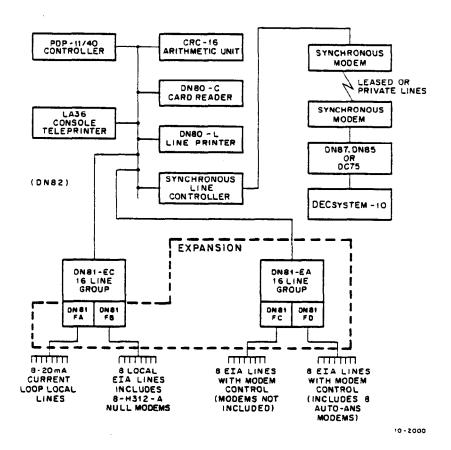

| 4-9        | DN80-Series Remote Station                               | SYS10/4-68 |

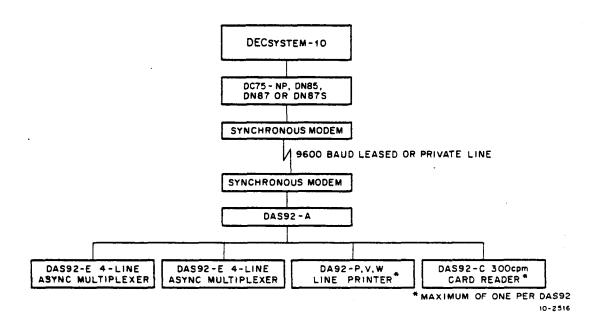

| 4-10       | DAS92 Remote Station (Typical Configuration)             |            |

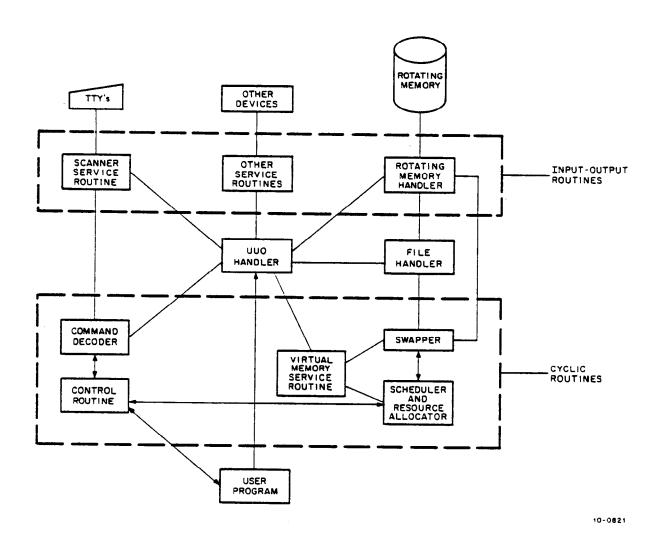

| 5-1        | The Resident Operating System                            |            |

|            | TABLES                                                   |            |

| Table No.  | Title                                                    | Page       |

| 4-1        | Interleaving Configurations                              | SVS10/4-29 |

| 5-1        | File Protection Scheme                                   |            |

M0607

DECsystem 1080/1090

This manual contains the system level technical description of the DECsystem-1080/1090, the KL10-A/B-based machines. The companion interface and unit level technical descriptions and other related manuals are identified in the document titled *Introduction to KL10-Based System Technical Description* (EK-KL10-TD-XXX). There are five sections in this manual. It provides an integrated hardware/software systems presentation with appropriate conceptual overviews of time-sharing/batch operation, DECsystem-10 principles, and system features. The five sections comprising this system level presentation are:

- 1. Principles of Time-Sharing

- 2. DECsystem-10 Primer

- 3. System Features

- 4. The Hardware

- 5. The Software

The purpose of this manual is to provide a comprehensive overview of the KL10-based DECsystem-10 machines. Intended target population is field service, manufacturing, and customer training personnel and students.

# SECTION 1 PRINCIPLES OF TIME-SHARING

#### 1.1 INTRODUCTION

Early computers were the province of the mathematician. Used mainly to solve differential equations, the systems were narrow in scope and poorly used. Because few persons were knowledgeable enough to employ the enormous processors, one individual could monopolize computer time – sit at the console and solve problems in step-by-step fashion.

As more people discovered computing techniques, it was no longer practical to let a few persons monopolize computer time. To increase machine efficiency, batch processing was introduced. In this mode of operation, no time was wasted between jobs. Programs were punched on cards and the cards stacked and fed to the computer in batches. Operation of each program was governed by control cards that took the place of the human operator.

Since card reading is a relatively slow process, some early systems employed a small computer to read the cards and transfer program information to magnetic tape that was then input to the large computer. As a further refinement, programs were assigned priorities, with short jobs being executed first to minimize job turnaround.

But what about the computer user? As computer utilization improved, program development took more time. To develop a new program, a user performed the following procedure:

After writing the program on paper, he carried it to a keypunch operator to have the cards punched and verified. A day or so later, when the program was returned, the user checked for punching errors, then returned the cards to the keypunch operator for corrections.

Next, he sent the cards to the computer center for compilation. The compilation, which might not be returned for a half day or more, could reveal spelling or syntactical errors. The cards then had to be changed and resubmitted – another half day's wait. If the next compilation was successful and the program was run, program logic errors might be discovered, meaning new cards, new compilation, etc. In addition, the user often studied reams of computer listings to find the errors. Using these inefficient methods, even simple programs might take weeks to develop.

Batch processing maximizes machine efficiency in routine data processing operations where turnaround is not critical. But for program development and modification, the user requires another mode of operation. The user needs a way to "interact" with the computer – to feed his program to the system, line-by-line, and continuously check the results. In fact, the user may want to develop interactive programs. These programs, which are extremely productive tools, ask the user questions and perform an analysis based on his answers. Electronic circuit design programs are a prime example. The computer actually designs the circuit by asking the engineer questions and formulating and manipulating data based on the answers. In addition, interaction provides a new dimension in management information reporting. Via an interactive terminal, a manager can request summaries, plot trends in plant operation and sales, and select special data for use in decision making.

If the user had unlimited funds, he might be tempted to buy or lease a large computer system he could dedicate to his work that would provide sufficient power, many peripherals, and a large variety of software. With such a system, the user could develop programs interactively or utilize batch processing for routine tasks. However, costs normally preclude the dedication of a large system to a single user.

By using time-sharing, the user has most of the benefits of a dedicated system at a small fraction of the cost. Time-sharing, with today's technology, allows a large powerful computer to handle 10, 50, 100, or more users simultaneously. Through a choice of terminals, the user can interface with the system or initiate batch processing which runs concurrently. The user also has access to a choice of mass storage devices and other peripherals as well as a selection of languages and application programs. Since response is fast, the user appears to have a dedicated system; yet costs are shared. Each user pays only for the time and facilities that he requires and does not pay for the time the machine is idle.

#### 1.2 OPERATION

A time-sharing system is not just any computer with some additional hardware and software. It is a system such as DECsystem-10 designed specifically for time-sharing in an interactive computing environment. Otherwise, facilities are limited, fewer users can be handled efficiently, and the economics are unattractive. At a minimum, a time-sharing system requires a central processor with sufficient speed and power, input/output terminals, and an amount of main memory (core or semiconductor) adequate to hold several users.

In a simple time-sharing system, each program is assigned a fixed time slice (time quantum) and operation is switched from one program to another in round robin fashion until each program is completed. Essentially, if each user receives 1/60 of a second and 12 users are "on" the system, each user will receive service every 1/5 of a second.

The time-sharing system performs interactive multiprogramming; that is, it allows several programs to reside in main memory simultaneously and to operate sequentially. The switching between programs, called context switching, is initiated by a clock which interrupts the central processor to signal that a certain time period has elapsed. The interrupt function is provided by a priority interrupt system. A monitor, also called an operating system or executive program, directs the execution of these tasks and performs other housekeeping duties.

The monitor is also involved in keeping the actions of a user within his assigned memory space. An address mapping scheme where a page table containing the address and access keys is set up by the monitor, limits the core area that a particular user can access. Any attempt by the program to read or change information outside that limit will automatically stop the program and notify the monitor.

The system discussed so far services a number of users sequentially in round robin fashion. To increase the number of users serviced, more main memory is required. However, since core is expensive, a secondary memory is employed. This memory – usually magnetic disk or drum – is slower than core or main memory but provides greatly increased capacity at reasonable cost. User programs can be located in secondary memory and moved into main memory for execution. Programs entering main memory exchange places with a program (or programs) that has just been serviced by the central processor. This operation is called swapping (Figure 1-1).

Figure 1-1 Swapping of User Programs

In operation, main memory is divided into separate memory blocks (modules). Secondary memory is connected to these modules through a high-speed input/output processor – a hardware device that allows the disk or drum to swap a program into any one of the main memory modules without any aid from the central processor. This structure allows the central processor to be operating a user program in one module of memory while programs are being swapped to and from another module. This independent overlapped operation, which greatly improves efficiency and processing power, is characteristic of an asynchronous system design philosophy (Figure 1-2).

Figure 1-2 Memory Structure

#### 1.2.1 Dynamic Scheduling

Round robin scheduling, in which each program operates in sequence and receives a fixed amount of time, is effective only if all programs have similar requirements. Such is not the case, however. At any particular time, a time-sharing system will be handling some programs which require extensive amounts of computing time (and are said to be compute bound) and other programs that must stop frequently for input or output (I/O bound).

To serve programs at and between these two extremes, the scheduling algorithm must provide frequent service to I/O bound programs and must give compute bound jobs longer time quantums (time slice) to prevent wasteful swapping. A simple dynamic scheme could provide two queues – one for each type of job. When a user first logs onto the system, he is placed in an I/O bound queue (waiting line) where he receives frequent service and small time quantums. If the program is not completed or does not request input or output during the time allotted, the job needs more computing time and is placed in the compute bound queue. Thus, the scheduling algorithm optimizes system efficiency by automatically adjusting to program requirements.

In the present state of scheduling art, algorithms are constantly being changed and improved. Current algorithms are extremely sophisticated, providing excellent service for most time-sharing job mixes. They also allow fine tuning, if such modifications are necessary. The ability of the algorithm to match processing to program requirements ensures the best service possible for all user programs.

In an efficient time-sharing system, monitor functions (referred to as monitor overhead) take 5 to 10 percent of central processor time, making 90 to 95 percent of the time available to users.

#### 1.2.2 Software Sharing

Since users of large time-sharing systems have varying requirements, a good system provides a wide variety of software – interactive languages such as BASIC and AID for the computations of the engineer and scientist, FORTRAN for more complex calculations, COBOL for data processing functions. Therefore, many users can have compilers and other common programs in core at the same time.

To prevent excessive core usage that results when a program is duplicated for several users, reentrant software is employed. That is, the program is written in two parts. One part contains pure code (reentrant code) that is not modified during execution and can be used to simultaneously service any number of users. For example, the pure code portion of FORTRAN can service multiple FORTRAN users. A separate, second part of the program belongs strictly to each user and consists of the code and data that is developed during the compiling process (impure code). This section is stored in a separate area of core. A comparison of memory usage in the non-reentrant and reentrant systems is shown in Figure 1-3.

Figure 1-3 Software Types

What are the benefits of reentrant software? First, less core is required. For example, a reentrant system can service three FORTRAN users with one 8K compiler and three 2K user areas, a total of 14K. A non-reentrant system would require 30K for the three 8K compilers and three 2K user areas. Total savings in this case is 16K of core. Using less core means that more programs can fit into a given amount of space. The monitor then swaps less often and spends less time swapping the smaller impure sections.

There are other savings too. Since the pure code never changes, it does not have to be returned to disk storage (swapped out). As long as a single copy is maintained on the disk, it can be called into core at any time. Programs can be swapped in or "overlaid" on top of the compiler to take its place in core whenever the compiler is not needed.

To protect the pure code from being modified, an address mapping feature, the pager, is implemented. This feature allows a program to execute as two separate segments where the pure segment is protected. User programs can also be written to make use of this protection. For example, a user might develop a reentrant information retrieval system written in COBOL.

#### 1.2.3 Communications

Communication between the remote user and the computer passes over the conventional dial-up telephone network. User terminals can therefore be located anywhere that phone service is available and connected to any computer system; feasibility is limited only by long distance phone rates.

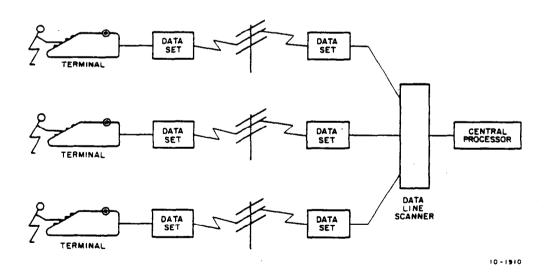

Each user terminal is connected to a data set or modem (modulator-demodulator) which converts user terminal output into a signal suitable for the telephone network. At the computer end of the phone lines, there is another data set which reconverts the signal and feeds it to a device called a data line multiplexer or data line scanner. This device, in turn, feeds the information from a number of terminals to the central processor (Figure 1-4).

Figure 1-4 User/Computer Communications

The number of data sets employed at the user end of the system is unlimited. At the computer end of the communications network, however, the number of data sets is limited by the number of users that can be serviced simultaneously by the system.

In order to gain access to the system, the user dials the system phone number from his data set. The telephone network handles the call, scanning the data sets at the computer system. If all of the sets are busy, the user receives a busy signal, just as he would with normal phone service. If a set is available, the telephone network rings it, causing the data line scanner to interrupt the monitor. The computer answers the call, placing the user in communication with the monitor. The terminal is then on-line and ready for operation.

#### 1.2.4 Control of Input/Output

A time-sharing system has performed its basic function if it allows a number of users simultaneous access to a central computer. However, to be fully useful, the system should also allow the users access to other system resources – storage devices for his programs and data, line printers, card readers, etc. For example, the user should be able to choose between magnetic tape and disk for program storage. If he has a 50-page report to produce, he should be able to employ a line printer instead of his terminal. If users controlled these devices, however, much confusion might result.

To prevent users from interfering with each other, the monitor coordinates input and output (I/O). The processor has an operating mode switch (user/executive mode) which the monitor sets before a user program is run. If the program attempts to perform input or output while in the user mode, the user program is stopped and the monitor takes over. Control thus diverted to the monitor is called **trapping**. When input/output is prevented or trapped, the computer is said to be in user mode; when I/O can be performed, the system is in executive or monitor mode.

User-to-monitor-mode switching occurs when the user requests I/O or other special functions to be performed by the monitor. The requests are made by using computer instructions referred to as monitor calls or programmed operators.

The monitor can also optimize throughput, keeping all devices busy simultaneously (overlapping of I/O operations) and executing jobs in the most efficient order. For example, it will start the read mechanisms on several disk packs in motion, simultaneously, to reduce the time required to find the desired data on each pack (access time). In addition, by means of the disk pack controller, the monitor can determine which of all needed data on a pack is closest to the read mechanism and can be obtained in the shortest amount of time (latency optimization).

#### 1.2.5 File Handling

If a user does not require a fast device for his exclusive use (private device) he can elect to use a public device and, in effect, perform time-sharing with a disk or drum. Under these conditions, user programs and data coexist on the device. Therefore, a filing system is necessary if program and data segments are to be retrieved in proper order.

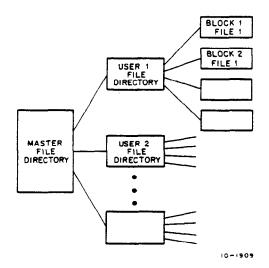

Data is transferred from memory to a peripheral device as a block of words or record. (A word is the number of binary digits or bits that the central processor can retrieve and "operate on" at one time.) Record length can be arbitrary or dictated by the physical device being used, e.g., the number of columns on an 80-column card or on a 132-column line printer. For DECsystem-10 disk files, the length is 128 words, so that blocks of 128 words are written at one time on a disk or other similar device.

For convenience each user's blocks are organized in groups called files which are listed in proper order in a special block on the disk called the users' file directory (UFD). A master file directory (MFD) is then required to maintain the locations of the UFDs and also keep track of the number of blocks of free storage that can be assigned to new files. The resulting hierarchy is shown in Figure 1-5.

Figure 1-5 File Structure

Files, like memory, must be protected from access by unauthorized users. When a user creates a file, he can restrict it, specifying whether others can have access, and if access is permitted, whether the files can be modified or only read. With such an arrangement, programmers in various plant locations can use the same data to work simultaneously on the same project, but unauthorized personnel cannot modify or read the files.

#### 1.2.6 Slow Peripherals

Fast peripherals can be time-shared. But what about the slow peripherals, such as the line printer and the card reader? Should other users be required to wait 20 minutes or so while one user ties up the line printer?

To eliminate conflicts, the user can request a slow device for his exclusive or private use. For example, he can request the line printer or card reader. Also available for private use are removable storage devices such as magnetic tape, DECtape (DIGITAL's low cost, high reliability magnetic tape), or disk packs. If the device is not already assigned to another user, the monitor, in cooperation with the operator, grants his request and the user has the device at his disposal until he releases it or logs off the system. For example, the user could request the use of multiple disk pack drives (exclusive use) to sort a payroll transaction file, or he could assign himself a DECtape drive and ask the system operator to mount the DECtape that contains his own personal library of programs.

Spooling is another method for handling data to or from slow peripherals. In this method, the slow device is simulated by a fast peripheral such as a disk. That is, all output for the line printer or card punch is deposited on the disk. The data on the disk is later "unspooled," with a special program transferring information to the slow device.

A program that has data for a slow device thus waits only milliseconds while the data is being deposited on a disk, instead of minutes or hours for a turn at the line printer. Input from slow devices can also be spooled, a particularly useful method for batch processing.

#### 1.3 RELIABILITY

With a large number of users depending on its operation, the time-sharing system must be extremely reliable. A system with 99 percent reliability can be "down" 14 minutes during a 24-hour working day. If that 14 minutes affects only one user, reliability may be acceptable. However, if it affects a large number of users, the consequences are more serious.

The problem is also complicated by the fact that reliability is a function of both hardware and software. It may take years, for example, to experience all the events that could uncover an error in software as complex as a time-sharing monitor.

Today's hardware and software has reliability built in. Hardware is designed in modular fashion so that failed components can be removed and new replacements "plugged in." Some components also contain self-testing features that detect potential failures. Software is designed to be "defensive"; that is, it anticipates certain types of failures and helps to minimize their effects. For example, the software might note parity errors and limit their effect to the program being operated.

Diagnostic software can run routinely as one of the time-sharing users. Software can also maintain a log of failures, so that patterns can be established and problems remedied before serious damage occurs. Systems that employ these reliability techniques keep downtime at a minimum.

### SECTION 2 DECsystem-10 PRIMER

#### 2.1 INTRODUCTION

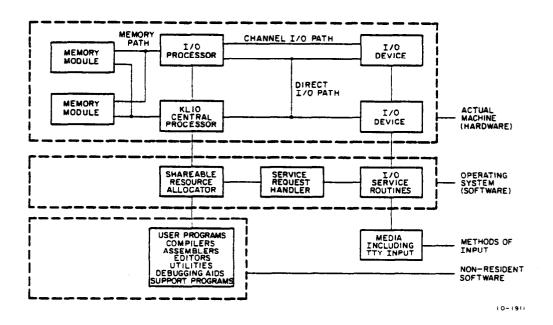

The DECsystem-10 is more than a processor and its associated peripheral devices. Because it is a system, there are many parts, or components, working together to achieve a goal in a manner that is both convenient for the user of the system and advantageous for the operation of the system. It is a machine designed to be utilized concurrently by many users who wish to perform various operations. There are three major components of the computing system, as shown in Figure 2-1: the actual machine, or hardware; the operating system, or monitor; and the languages and utilities, or non-resident software.

Figure 2-1 DECsystem-10 Components

#### 2.2 HARDWARE

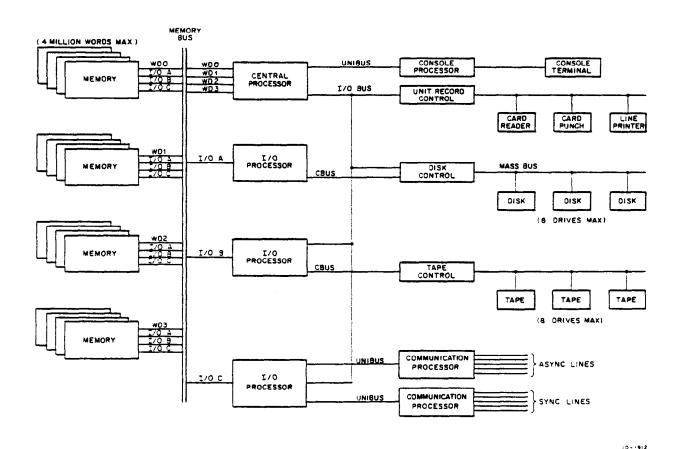

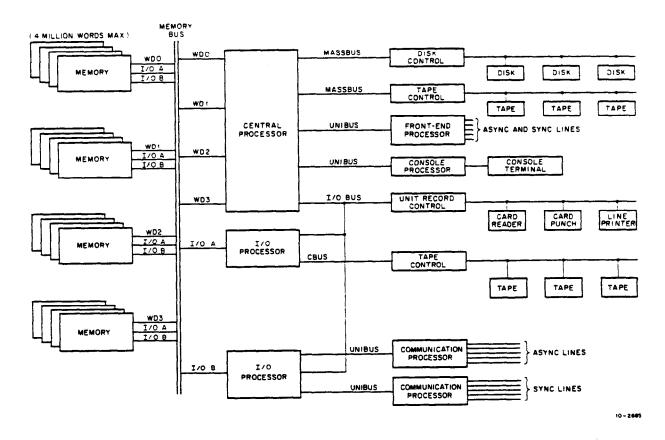

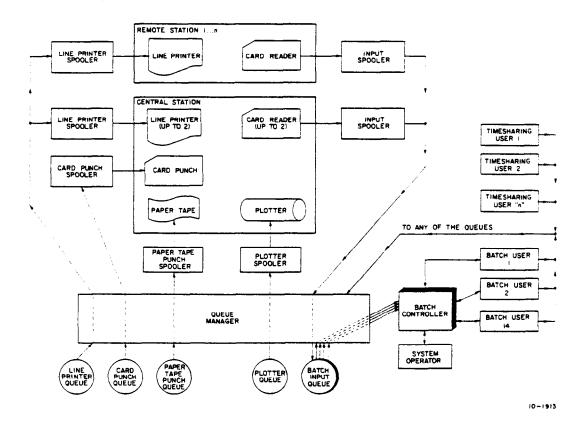

The DECsystem-10 hardware consists of one or two central processors, various I/O processors, and various memories and input/output devices. There are now 11 basic system configurations included in the DECsystem-10 family; each configuration is distinguished by the hardware associated with the type and number of central processor and the type and number of I/O processors. By adding hardware to an individual system, additional performance is achieved. However, when adding hardware to expand from a small system to a larger system, no software changes are required in user programs. A single operating system and command control language can be used for all configurations of the DECsystem-10. Simplified block diagrams illustrating the 1080 and 1090 systems (the KL10-based systems) are shown in Figures 2-2 and 2-3.

Figure 2-2 A Typical DECsystem-1080

Figure 2-3 A Typical DECsystem-1090

#### 2.3 OPERATING SYSTEM

The DECsystem-10 hardware has numerous capabilities: it is powerful, fast, and highly sophisticated. Because of its complexity, this machine is not usually manipulated directly by its users. The users communicate with an intermediary, the operating system, in order to direct their problems to the actual machine and to receive solutions back. With many users on the system, this second component of the DECsystem-10 must also keep track of what each user does and the devices and system resources that each user accesses. Though the operating system cannot be seen like the actual machine, the action of the operating system is the most important and noticeable part of the system to each user. It is true that the operating system can do nothing for the user if the actual machine does not exist, but the user normally does not think of this. If the operating system accomplishes for him what he wants the actual machine to do, he is satisfied. Therefore, it is important to the user that he depend on the same operating system regardless of the hardware that composes the actual machine.

The operating system is always resident in main memory of the actual machine and is composed of three parts (Figure 2-1). Because there are so many services that can be obtained from the operating system, including the allocation of core memory, processor time, and devices of the actual machine, one part, the service request handler, is responsible for accepting requests for these services. The service request handler passes the requests to another part, the sharable resource allocator, which is responsible for allocating the services requested. If the requested service is for use of a device, the I/O service routines are then notified to carry out the user's request.

#### 2.4 NONRESIDENT SOFTWARE

The third component of the DECsystem-10 is the nonresident software, those programs necessary for the varied operation of the computing system. This software includes the compilers, assemblers, editors, debugging programs, and operating system support programs. These software programs reside on a high-speed mass storage device of the actual machine and are brought into memory when needed by a user. By utilizing the nonresident software, the user of the computing system can create programs, transfer them from one device to another, compile, edit, execute, and debug them, and then receive the results of execution on any specified device.

#### 2.5 MULTIPROCESSING

The DECsystem-10 can be a single-processor system or a dual-processor system, composed of a primary processor and a secondary processor. Each processor in the dual-processor system runs user programs, schedules itself, fields instruction traps, and processes most requests to the operating system. In addition to these tasks, the primary processor also has control of all the input/output devices. This is because only the primary processor has access to the I/O bus. The primary processor completes any job that the secondary processor could not finish because of an I/O request to the operating system. Both processors are connected to the same memory and execute the same copy of the operating system, thereby saving core memory over a multiprocessing system in which each processor has its own copy.

The primary objective in the DECsystem-10 dual-processor environment is to provide more processing power than that found in the single-processor DECsystem-10. This means that with the addition of the second processor, more users can run at the same time. If more users are not allowed on the system, the addition of the second processor reduces the elapsed time required to complete the processing of most programs.

#### 2.6 MULTIMODE COMPUTING

The DECsystem-10 is designed for the concurrent operations of time-sharing, multiprogram batch, real-time, and remote communications in either single- or dual-processor systems. In providing these multifunction capabilities, the DECsystem-10 services interactive users, operates local and remote batch stations, and performs data acquisition and control functions for on-line laboratories and other real-time projects. By dynamically adjusting system operation, the DECsystem-10 provides many features for each class of user and is therefore able to meet a large variety of computational requirements.

#### 2.6.1 Time-Sharing

Time-sharing takes maximum advantage of the capabilities of the computing system by allowing many independent users to share the facilities of the DECsystem-10 simultaneously. Because of the interactive, conversational, rapid-response nature of time-sharing, a wide range of tasks – from solving simple mathematical problems to implementing complete and complex information gathering and processing networks – can be performed by the user. The number of users on the system at any one time depends on the system configuration and the job mix on the system. DECsystem-10 time-sharing is designed to allow for up to 150 command terminals. Interactive terminals can include CRTs, hard copy terminals, and other devices which operate at speeds of 110 to 9600 baud. Terminal users can be located at the computer center or at remote locations connected to the computer center by communication lines.

Time-sharing on the DECsystem-10 is general-purpose, i.e., the system is designed in such a way that the command language, input/output processing, file structures, and job scheduling are independent of the programming language being used. In addition, standard software interfaces make it easy for the user to develop his own special language or systems. This general-purpose approach is demonstrated by the many special-purpose programming languages implemented by DECsystem-10 users.

2.6.1.1 Command Language – By allowing resources to be shared among users, the time-sharing environment utilizes processor time and system resources that are wasted in single-user systems. Users are not restricted to a small set of system resources, but instead are provided with the full variety of facilities. By means of his terminal, the user has on-line access to most of the system's features. This on-line access is available through the operating system command language, which is the means by which the time-sharing user communicates with the computing system.

Through the command language, the user controls the running of his job, or task, to achieve the results he desires. He can create, edit, and delete his files; start, suspend, and terminate his job; compile, execute, and debug his program. In addition, since multiprogramming batch software accepts the same command language as the time-sharing software, any user can enter his program into the batch run queue. Thus, any time-sharing terminal can act as a remote job entry terminal.

- 2.6.1.2 Peripheral Devices With the command language, the user can also request assignment of any peripheral device, e.g., magnetic tape, DECtape, and private disk pack, for his own exclusive use. When the request for assignment is received, the operator verifies that the device is available to this user, and the user is granted its private use until he relinquishes it. In this way, the user can also have complete control of devices such as card readers and punches, paper tape readers and punches, and line printers.